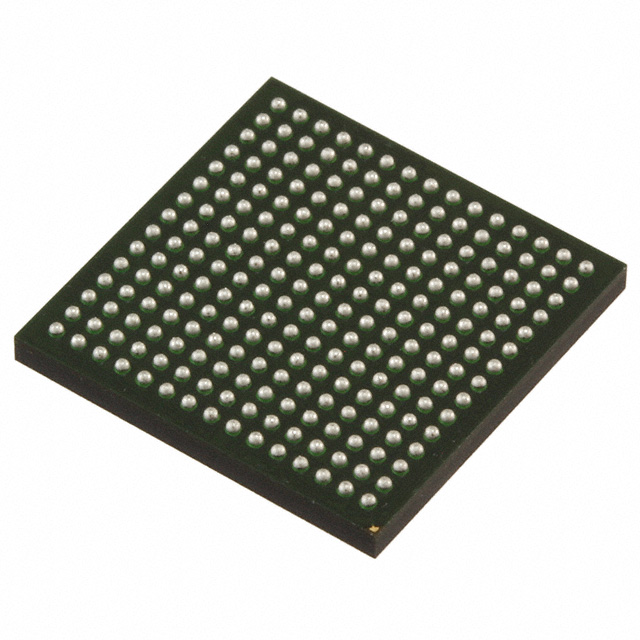

XC7Z007S-1CLG225I IC SOC CORTEX-A9 667MHZ 225BGA elektroniese komponente ic skyfies geïntegreerde stroombane eie voorraad BOM Service

Produk eienskappe

| TIPE | BESKRYWING |

| Kategorie | Geïntegreerde stroombane (IC's) |

| Mnr | AMD Xilinx |

| Reeks | Zynq®-7000 |

| Pakket | Skinkbord |

| Standaard Pakket | 160 |

| Produk Status | Aktief |

| Argitektuur | MCU, FPGA |

| Kernverwerker | Enkele ARM® Cortex®-A9 MPCore™ met CoreSight™ |

| Flits grootte | - |

| RAM grootte | 256KB |

| Randapparatuur | DMA |

| Konnektiwiteit | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Spoed | 667MHz |

| Primêre eienskappe | Artix™-7 FPGA, 23K logiese selle |

| Werkstemperatuur | -40°C ~ 100°C (TJ) |

| Pakket / houer | 225-LFBGA, CSPBGA |

| Verskafferstoestelpakket | 225-CSPBGA (13×13) |

| Aantal I/O | 54 |

| Basisproduknommer | XC7Z007 |

China keur AMD se verkryging van Xilinx goed met 5 voorwaardes!

Op 27 Oktober 2020 het AMD aangekondig dat hy Xilinx (Xilinx) vir VS$35 miljard sal verkry in 'n transaksie met alle aandele.Die transaksie, hoewel eenparig deur die direksies van albei partye goedgekeur, moet steeds deur aandeelhouers van albei partye goedgekeur word, met regulatoriese goedkeuring van verskeie lande, insluitend, natuurlik, China.

Onlangs het die Anti-Monopoly Buro van China se Staatsadministrasie van Marktoesig en Administrasie die besluit aangekondig om die anti-monopolie hersiening van die verkryging van 'n belang in Xilinx deur Chaowei Semiconductor Corporation met bykomende beperkende voorwaardes (die "Aankondiging") goed te keur, goed te keur. die verkryging van Xilinx deur AMD en die verwydering van die finale regulatoriese hekkie vir die verkryging.

Volgens die aankondiging, na 'n jaar van ontvangs van die anti-monopolie verklaring van operateur konsentrasie in die geval van AMD se verkryging van Xilinx op 19 Januarie 2021, en die indiening van die saak nadat die aansoeker sy verklaring materiaal aangevul het, die Algemene Administrasie van Markregulering (GAMR) het besluit om die saak met beperkende voorwaardes goed te keur.

Samesmeltings word toegelaat, maar geen gebundelde verkope of diskriminasie teen Chinese kliënte nie

Dit is belangrik om te verstaan dat verkrygings met oorgrensbedrywighede regulatoriese goedkeuring van verskeie sleutelmarkreguleerders regoor die wêreld vereis.Voorheen het die VSA, die VK en die EU reeds die verkryging goedgekeur, en noudat China die saak goedgekeur het, beteken dit dat AMD sy verkrygingsplanne in die eerste kwartaal van 2022 sal kan voltooi.

Daar moet egter op gelet word dat die goedkeuring van AMD se verkryging van Xilinx deur die Chinese Algemene Administrasie van Markregulering gepaard gaan met bykomende beperkende voorwaardes, wat vereis dat beide partye by die transaksie en die na-konsentrasie-entiteit die volgende verpligtinge nakom.

(i) Wanneer SuperPower SVE's, SuperPower GPU's en Celeris FPGA's aan die mark in China verkoop word, sal hulle op geen manier gekoppelde verkope verplig of enige ander onredelike handelsvoorwaardes aanheg nie;hulle sal nie kliënte verhinder of beperk om bogenoemde produkte individueel te koop of te gebruik nie;en hulle sal nie diskrimineer teen kliënte wat die bogenoemde produkte individueel koop in terme van diensvlak, prys, sagteware-kenmerke, ens.

(b) Bevorder relevante samewerking verder gebaseer op die bestaande samewerking met ondernemings in China en gaan voort om Chaowei SVE's, Chaowei GPU's, Xilinx FPGA's en verwante sagteware en bykomstighede aan die mark in China te verskaf volgens die beginsels van billikheid, redelikheid en nie- diskriminasie.

(iii) Verseker die buigsaamheid en programmeerbaarheid van die Xilinx FPGA's, gaan voort om die Xilinx FPGA-produklyn te ontwikkel en te verseker, en verseker dat dit ontwikkel word op 'n wyse wat versoenbaar is met ARM-gebaseerde verwerkers en in ooreenstemming met Xilinx se planne voor die Transaksie .

(iv) voortgaan om die interoperabiliteit van Chaowei SVE's, Chaowei GPU's en Celeris FPGA's te verseker wat aan die mark in China verkoop word met derdeparty-SVE's, GPU's en FPGA's;die bogenoemde vlak van interoperabiliteit sal nie laer wees as die vlak van interoperabiliteit van Chaowei SVE's, Chaowei GPU's en Celeris FPGA's nie;inligting, kenmerke en monsters wat met die interoperabiliteitsopgradering verband hou, sal binne 90 dae na die opgradering van SVE, GPU en FPGA-vervaardigers aan die derde party verskaf word.

(v) Maatreëls tref om die inligting van die derdeparty-SVE-, GPU- en FPGA-vervaardigers te beskerm en vertroulikheidsooreenkomste met die derdeparty-SVE-, GPU- en FPGA-vervaardigers aan te gaan;stoor die vertroulike inligting van die derdeparty-SVE-, GPU- en FPGA-vervaardigers in aparte en wedersyds eksklusiewe hardewarestelsels.

.png)